# HEWLETT-PACKARDJOURNAL

# **HEWLETT·PACKARD JOURNAL**

Technical Information from the Laboratories of Hewlett-Packard Company

### **Contents:**

### AUGUST 1981 Volume 32 • Number 8

**200-kHz Power FET Technology in New Modular Power Supplies,** by Richard Myers and Robert D. Peck These 50W printed-circuit board supplies are highly reliable and meet worldwide safety standards.

**Magnetic Components for High-Frequency Switching Power Supplies, by Winfried Seipel** The goals were small size, 200-kHz operation, safety, and semiautomated manufacturing.

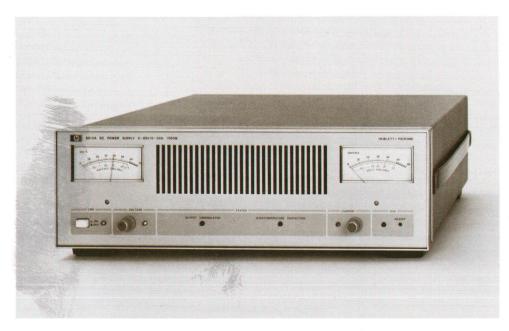

Laboratory-Performance Autoranging Power Supplies Using Power MOSFET Technology, by Dennis W. Gyma, Paul W. Bailey, John W. Hyde, and Daniel R. Schwartz These are precision 200W and 1000W supplies designed for a variety of laboratory, industrial, and systems applications.

The Vertical Power MOSFET for High-Speed Power Control, by Karl H. Tiefert, Dah Wen Tsang, Robert L. Myers, and Victor Li With current flowing vertically, more power can be switched without sacrificing switching speed.

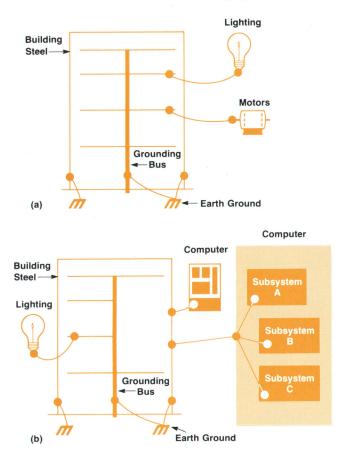

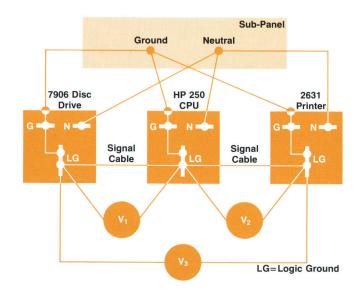

**Power Line Disturbances and Their Effect on Computer Design and Performance**, by Arthur W. Duell and W. Vincent Roland Proper site wiring, adequate grounding, and use of isolation devices help assure satisfactory performance.

### In this Issue:

When we plug something into an electrical outlet we are connecting it to a voltage that alternates between positive and negative values 50 or 60 times per second, depending on the country. This voltage may be subject to random noise and to large, unpredictable, sudden fluctuations as the utility company supplying us with electric power experiences demand variations, electrical storms, equipment problems, and other disturbances. Electronic circuits like those in television sets, computers, stereo systems, and electronic instruments don't like this kind of power. They need steady, well regulated, battery-like voltages. Large disturbances can disrupt or even destroy them.

The articles in this issue deal with the problems of changing unregulated alternating voltages to regulated battery-like ones, and of dealing with unpredictable power anomalies. The first two articles are about the design of some innovative new power supplies. Power supplies are electronic devices that convert what comes out of an electrical outlet to regulated voltages for other electronic devices to use. For example, there's a power supply inside every piece of electronic equipment. This kind of power supply should be small and as reliable as the wall outlet it's plugged into. The 65000A Series Modular Power Supplies (cover and page 3) are of this type. There are also power supplies that provide regulated voltages to circuits outside their own cabinets. These might be found sitting on a lab engineer's bench or mounted in a rack as part of a computer-controlled test system. These supplies should be extremely well regulated, accurate, and for some applications remotely programmable. Models 6012A and 6024A Autoranging Power Supplies (page 11) are in this category.

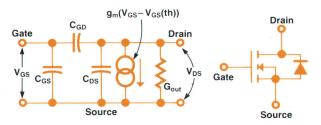

Although they are meant for different applications and represent different design approaches, both of these new power supply families take advantage of a new HP switching transistor called a power MOSFET (metaloxide-semiconductor field-effect transistor). MOSFETs have been around for a while and their superiority over other kinds of transistors for many high-frequency applications is well known. However, until recently there weren't any with the HP device's combination of high voltage rating, fast switching speed, low resistance, high reliability, and small chip size. The cover photograph shows where the HP power MOSFET fits in the schematic diagram of a 65000A Power Supply. On page 18 is an article about the new MOSFET, telling why it's different and how it's made.

The special problems power line disturbances cause computers (in spite of their well regulated power supplies) are discussed in the article on page 25. This article is based on studies of typical power line conditions, wiring codes for buildings, computer installation procedures, and computer designs. The article should be of interest to anyone who owns a computer system or is considering installing one.

-R. P. Dolan

C Hewlett-Packard Company 1981 Printed in U.S.A.

# 200-kHz Power FET Technology in New Modular Power Supplies

These small, reliable 50-watt supplies are designed for OEM (original equipment manufacturer) use anywhere in the world.

### by Richard Myers and Robert D. Peck

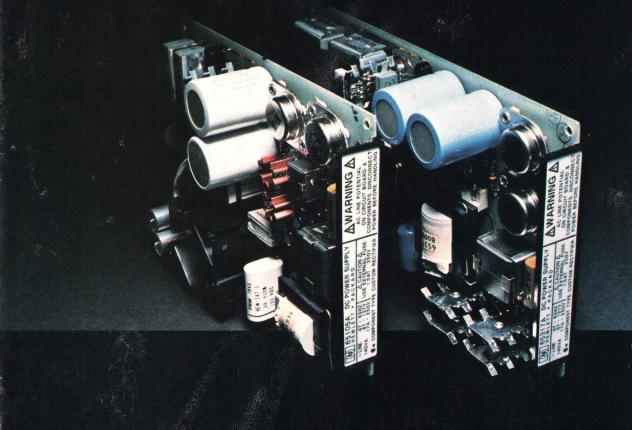

NEW HP-DEVELOPED fast-switching power fieldeffect transistor (FET) has made possible a new series of 50-watt printed-circuit-board power supplies that feature very small size, light weight, and demonstrated reliability of 100,000 hours mean time between failures (MTBF). Fig. 1 shows some of the eight models in the 65000A Series. They have one to six outputs in combinations of 5, 12, 15, and 18 volts dc. Intended for worldwide use, the supplies operate from both 120Vac and 240Vac power lines. They are UL-recognized in the U.S.A. (UL 478 and UL 114), certified by CSA in Canada (CSA 22.2 No. 143 and No. 154), and are designed to meet the requirements of VDE in the Federal Republic of Germany (VDE 0730 Part 2P) and IEC 348. They are brownout-proof and have remote shutdown terminals.

These power supplies are designed for use by original equipment manufacturers (OEMs) in modems, flexible disc drives, microcomputers, and many instruments. They meet OEMs' usually contradictory requirements for power supplies. For example, OEMs want low levels of electromagnetic interference (EMI) and conformance to safety regulations along with small size and weight. However, with most circuit schemes, meeting domestic and international EMI and safety requirements means large size and weight to accommodate EMI suppression components and safety spacings between and within components. OEMs also want complex system features such as remote shutdown and overvoltage, overcurrent, and overtemperature protection along with reliability and well regulated dc output voltages. Providing these features conventionally means complex circuits and therefore inherently lower reliability.

### **Design Approach**

The key ingredients that make it possible to meet these usually conflicting requirements are power MOSFET\* technology, a switching frequency of 165-200 kHz, and sine-wave power conversion.

HP has been designing and manufacturing conventional switching-mode power supplies for many years and their peculiar problems are well understood. For all their virtues, they suffer from several notable difficulties. They are capable of producing high levels of EMI, have complex timing requirements, particularly during turn-on and turn-off transients, and as a result are susceptible to catastrophic faults, and have resisted attempts to increase their frequency of operation beyond 50 kHz. Higher operating frequencies have been a temptation for several years; however, switching transistors suitable for operating frequencies beyond 50 kHz and operating voltages of 450V have not been readily available. Yet small size requires a much higher switching frequency.

Power MOSFETs were the needed solution. A program \*Metal-oxide-semiconductor field-effect transistor.

**Fig. 1.** *HP* 65000A Series Modular Power Supplies are small 50W dc supplies that have one to six outputs in combinations of 5, 12, 15, and 18 volts. The eight models in the series meet worldwide safety and EMI standards and are highly reliable.

was begun at HP to develop power FETs with characteristics suitable for off-line switching regulators (see article, page 18). However, it then became apparent that power switches were only part of the high-frequency problems. The construction of transformers that simultaneously meet worldwide safety requirements and have leakage inductance commensurate with standard pulse-width modulation techniques is no small matter. High-frequency operation of transformers in a conventional pulse-width modulation mode is difficult to achieve. If a transformer is designed to be thermally limited (fixed temperature rise) and its frequency of operation is increased, the per-unit leakage inductance of the transformer increases approximately as the square root of the frequency. Leakage inductance results in power dissipation in snubber circuits, EMI, increased open-loop output impedance, and increased stress on power semiconductors. Clearly, if high-frequency operation is desired some method of eliminating the undesirable effects of leakage inductance had to be found.

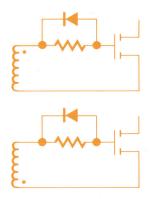

### Sine-Wave Voltage Regulation

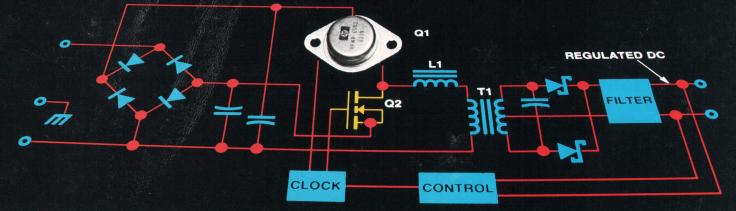

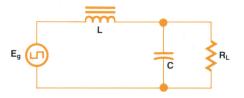

The power conversion and voltage regulation technique used in the 65000A Series eliminates many of the bad effects of leakage inductance. 165-to-200-kHz square waves are converted to sine waves as an integral part of the regulation process. This voltage regulation, technique can be explained with the circuit shown in Fig. 2. The circuit is a simple series resonant tank, and the voltage source  $E_g$  is a square-wave generator. The low-pass characteristic of the tank circuit effectively filters the square wave and converts it to a sine wave.

For the purpose of analysis consider the source to be a sinusoidal source whose output is equal to the magnitude of the fundamental component of the square wave. This approximation allows routine ac analysis to be used and simplifies the mathematics considerably.  $R_L$  represents the load connected to the output of the power supply, plus rectifier, switch, and magnetic losses. L and C are the energy storage elements of the resonant tank.

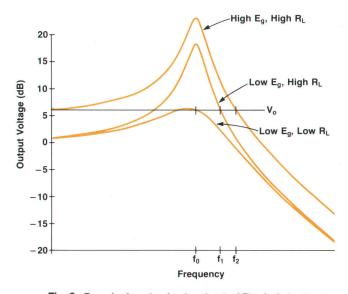

If the frequency of the generator,  $f_g$ , is equal to the resonant frequency of the tank and resistor  $R_L$  is sufficiently large, then the output voltage across  $R_L$  is a maximum. As the frequency of the generator is increased the output voltage falls asymptotically at 12 dB/octave, as shown in Fig. 3. If the generator is a voltage-controlled oscillator (VCO) whose minimum frequency of operation is the resonant frequency of the tank, the output voltage developed across  $R_L$  is easily controlled. Rectification and filtering of this output voltage generates the required dc output. As the load current drawn from the power supply decreases, the Q of

**Fig. 2** This simplified circuit illustrates the voltage regulation technique used in the 65000A Series Power Supplies. The tank circuit converts the square wave to sine waves as an integral part of the technique. See Fig. 3.

**Fig. 3.** Transfer function for the circuit of Fig. 2. Adjusting the frequency of the generator keeps the output voltage constant at  $V_o$  under varying line voltage and load conditions.

the resonant tank increases and the control circuit increases  $f_g$ , thus maintaining a constant output voltage.

Significantly, if the output is short-circuited ( $R_L=0$ ) the output current and the current in  $E_g$  are limited by the resonating inductor L. This inherent current-limiting mechanism is of great value in controlling faults and in simplifying control circuits.

Compared to the usual pulse-width-modulation switching regulated power supply, this sine-wave power conversion technique requires 25-33% fewer control and drive components. It also provides 15-20 dB less EMI than typical 50-to-100-watt open-frame switching power supplies.

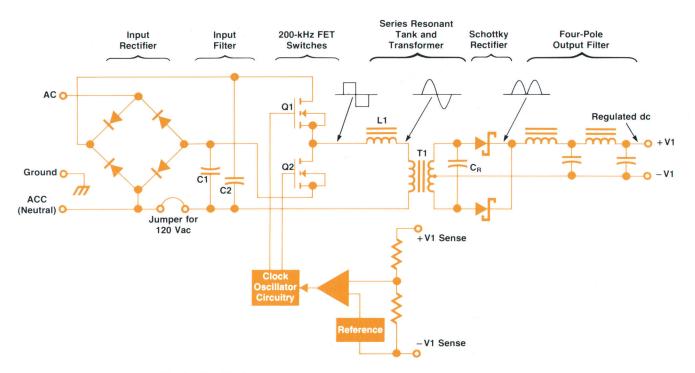

### **Power Supply Circuit**

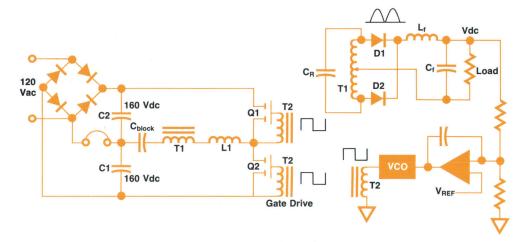

An implementation of this circuit for voltage regulation is shown in Fig. 4. It is shown operating directly from a 120Vac 60-Hz power line. After conversion from 60-Hz ac to unregulated dc, the dc output voltage is regulated by the method shown in Fig. 3.

In this circuit a bridge-doubler capacitor configuration is used to derive a  $\pm 160$ Vdc supply from the ac power line. This voltage is unregulated and contains a significant percentage of 60-Hz and 120-Hz ripple. Power FETs Q1 and Q2 provide the square wave by switching alternately.

The use of FETs is not arbitrary. Conventional bipolar transistors present very difficult problems because their storage time makes simultaneous conduction of Q1 and Q2 a certainty if they are driven with square waves (see Fig.4). Pulse-width modulators used in conventional switching supplies avoid square waves by inserting a dead time. Unfortunately, this use of dead time increases the complexity of the driver circuit. Because FETs do not have storage time, they can use a square wave and a simple drive circuit, with a reduced parts count and a consequent increase in reliability.

In Fig. 4, L1 is the resonating inductor and serves to insure that the voltage applied to transformer T1 is truly sinusoidal. Since the voltage rate of change (dv/dt) applied

**Fig. 4.** Simplified schematic of a 65000A-type off-line sine-wave converter.

to the transformer is significantly reduced by L1, the problem of EMI is dramatically lessened.  $C_{block}$  serves to insure that no dc current is allowed to circulate in T1.  $C_R$ , the resonating capacitor, appears on the secondary of transformer T1. Notice that this placement of  $C_R$  effectively puts the leakage inductance of transformer T1 in series with resonating inductor L1. A price is paid, however, for this tuning out of the leakage inductance. The rms current in the resonating capacitor is nearly the same as the dc output current. This made it necessary to develop high-current capacitors for the 65000A Series, as discussed later in this article.

Rectifiers D1 and D2 and the output filter ( $L_f$  and  $C_f$ ) constitute a conventional center-tapped full-wave rectifier and averaging filter. Significantly, the required inductor  $L_f$  is smaller than an equivalent filter inductor in a pulse-width modulator by a factor of nearly 2.5 to 1. This reduction is possible because sine waves are being filtered instead of a pulse train.

The filtered output voltage  $V_{dc}$  is compared to the desired output voltage  $V_{REF}$ , amplified and applied to a voltagecontrolled oscillator. The oscillator is used to drive the power FETs and regulate the output voltage. A special magnetic component developed for the oscillator allows the frequency of a square-wave oscillator to be controlled by varying the current in a winding. This control inductor was selected because of its simplicity, reliability, and ability to meet worldwide safety standards.

Several characteristics of this power supply circuit make it especially attractive for use in the 65000A Series. It uses a simple and reliable control technique with standard linear circuits and without recourse to complex and unwieldly pulse-width circuits. It has inherent current limiting that requires no additional circuitry. A short on the output rectifiers, resonating capacitors, or transformer will actually produce a decrease in the FET current.

High-frequency operation can be easily achieved. The 65000A Series operates at frequencies in excess of 200 kHz and is designed to meet worldwide safety specifications. The output choke in the output averaging filter is 2.5 times smaller than an equivalent choke in a pulse-width modulated unit. EMI problems are minimized because of the presence of sinusoidal waveforms at all points beyond the resonating inductor L1. The simple control techniques result in a lower parts count and a much improved MTBF

(greater than 100,000 hours MTBF demonstrated for a single-output unit with 395,000 unit hours of life tests).

The disadvantage of the circuit is that it requires an extra magnetic component (resonating inductor L1) and a resonating capacitor  $C_R$ . However, this disadvantage is more than compensated by the sharp reduction in size resulting from the increased frequency of operation (almost 10:1).

### **Voltage-Controlled Oscillator**

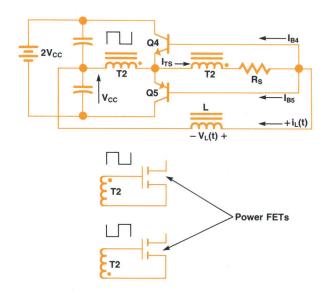

The novel voltage-controlled oscillator provides more than one ampere of drive current to the FETs using only eight components. It is an inductively coupled, astable multivibrator. A simplified circuit diagram is shown in Fig. 5.

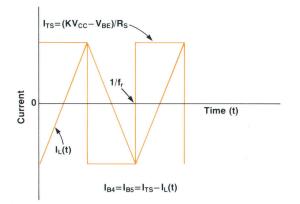

To understand the oscillator's operation assume that transistor Q4 is conducting. The current  $I_{TS}$  is equal to  $(KV_{CC} - V_{BE})/R_S$  and is constant. Because  $V_{BE}$  is positive, transistor Q5 is held off and voltage  $V_{CC}$  is applied to the primary of transformer T1. The voltage  $V_L(t)$  is positive and results in an increasing current  $i_L(t)$  and eventually  $I_{TS}$  =

**Fig. 5.** High-current voltage-controlled oscillator (VCO) provides more than one ampere to drive the power MOSFETs, using only eight components. L is a variable control inductor; the oscillator frequency is controlled by varying the inductance of L.

**Fig. 6.** Current-time relationships in the voltage-controlled oscillator of Fig. 5.

$i_L(t)$ . This results in zero base current for Q4, which forces it to turn off regeneratively. Since  $i_L(t)$  is still positive, transistor Q5 is turned on very hard, resulting in a sharp voltage transition on transformer T2. Fig. 6 shows the current relationship.

The frequency of operation of this oscillator is given by the expression

$$\mathrm{f_r} ~\approx \frac{\mathrm{R_S}~(\mathrm{V_{CC}} + \mathrm{V_{BE}})}{4\mathrm{L}\,(\mathrm{KV_{CC}} - \mathrm{V_{BE}})}$$

Notice that because Q4 is turned off completely before Q5 is turned on, there is no possibility of simultaneous conduction of transistors Q4 and Q5. As a result, this oscillator is capable of driving heavily capacitive loads with a very respectable square wave at frequencies in excess of 200 kHz. The frequency of the oscillator is varied by controlling the effective inductance L. This variable control inductor appears schematically in Fig. 7. An especially useful feature of the variable control inductor is that very little of the ac voltage generated on the primary of the inductor (the oscillator side) is reflected to the control winding. The variable control inductor is described in more detail on page 8.

Power FET gates make good loads for drive circuits because of their high impedances. In addition, FETs eliminate concern about storage time. As a result, a FET drive circuit is very simple, as shown in Fig. 8. The resistor-diode networks in the drive circuit provide a small delay between turn-on and turn-off of the power FETs. This helps reduce switching losses.

### **Simplified Power Supply Schematics**

The simplified schematic of Fig. 9 shows a single-output supply. The 320V peak-to-peak square wave output from

**Fig. 7.** Simplified schematic of the variable control inductor shown in Fig. 5.

Q1 and Q2 drives the series resonant circuit consisting of inductor L1, the leakage inductance of transformer T1 and the reflected capacitance of capacitor  $C_R$ . The nominal frequency of the clock driving the FETs is higher than the circuit's resonant frequency. Regulation is by frequency modulation. When the control circuit slows down the clock and the FET switching rate, the voltage across capacitor  $C_R$  increases and thus increases the rectified and filtered output voltage V1. When the clock speeds up, output voltage V1 decreases. The control circuit adjusts the frequency to provide 0.1% line and load regulation for V1.

The schematic of Fig. 10 shows how multiple output voltages are implemented and how 120/240Vac dual power line capability is included. Fig. 10 also shows the bias supply and protection circuitry.

Output voltages V2 through V5 of this multiple-output model are derived as shown in the lower right of the figure. Semiregulated outputs V2 and V3 are the rectified and filtered outputs from an extra secondary winding on transformer T1. Outputs V4 and V5 are powered by V2 and V3 and provide 2% line and load regulation. The resonating capacitor function is now shared by two capacitors, C4 and C5.

### **Power FETs**

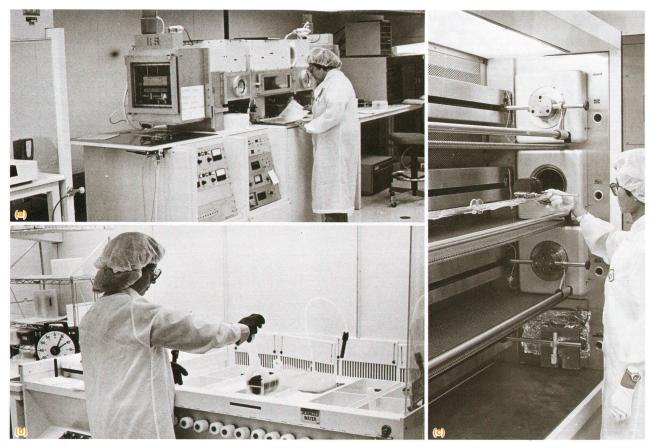

The power FET and the 65000A Series Power Supplies were developed together. When the 65000A project began only one power FET was being developed commercially and it was low-voltage (90V), extremely expensive, and had both reliability and delivery (manufacturing) problems. The requirements for a high-voltage (450V) power FET were analyzed by HP's central research labs, and it was concluded that the necessary production technologies existed and that FETs could be competitive with highvoltage bipolar transistors. The design and manufacture of a series of power FETs began at the central research labs.

The New Jersey Division assisted by setting up HP's first TO-3 packaging operation, by designing and building the high-voltage test equipment, and by setting up reliability test equipment for power semiconductors. Recently the Microwave Semiconductor Division has picked up responsibility for design, manufacture and packaging of the power FETs and now has its own test and reliability evaluation equipment.

The design and development program for the power FET

**Fig. 8.** Power FET drive circuit can be very simple because the FETs have high impedance and no storage time problems.

Fig. 9. Simplified schematic of a single-output 65000A Series Power Supply.

was different from a development program for a typical high-voltage power transistor. The performance of a FET can be accurately predicted and so the extensive experimentation and redesign that characterize bipolar development programs were not necessary. Along with predictable performance, manufactured FETs have consistent gains and switching speeds. Consistency and predictability are major advantages of FETs over bipolar power transistors and were crucial in the decision to develop a power FET just for switching power supplies.

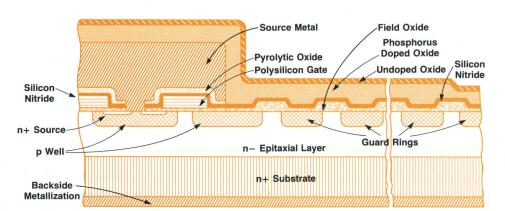

While the electrical performance was predictable, the challenge for the research labs was to develop HP's firsthigh-voltage manufacturing process and make reliable FETs. A high voltage rating of 450 volts is necessary for any off-line power supply designed to operate from 240Vac as used in Europe. A high voltage rating requires highresistivity silicon, which leads to high on resistance. Since high on resistance is undesirable, the FET production process has to be precisely controlled so that every FET has a voltage capability that is high enough, but not too high-470 to 530 volts is the permitted range. Another problem is that high voltages cause strong fields inside the FETs. These fields move any mobile ions present and thus change the threshold voltage and increase the drain leakage current, possibly causing power supply failures. Mobile ions can result from contamination, so the FET manufacturing process must be very clean to reduce their number.

From the beginning of the project reliability was a major concern. A reliability demonstration of 500,000 hours was required before the FETs would be used in the 65000A Series Power Supplies. The time required for the demonstration was compressed by a factor of about 25 by testing at  $175^{\circ}$ C instead of the  $125^{\circ}$ C maximum temperature rating. After considerable effort by the research labs, the FETs passed the 1000-hour test with just two failures in 140 devices. With each process change by any vendor these tests are repeated. Samples are taken from lots and given similar reliability tests. In this way continuing reliability is assured.

The power FETs have met the original goals. They have the required voltage, low on resistance, fast and consistent switching speeds, consistent gains, good manufacturing yields, and reliability. This contrasts with and is a welcome improvement over the performance of high-voltage bipolar transistors.

### **Film Capacitors**

The resonant circuit regulation scheme of the 65000A Series calls for a high-current film capacitor. The current in the capacitor is about 90% of the output current. This capacitor, required on the secondary of transformer T1 ( $C_R$  in Fig. 4), is physically large. Its operating current approaches the wire lead current rating and exceeds most manufacturers' current ratings for the capacitor winding end connections.

There were no commercially available capacitors with sufficient current ratings. Because the capacitor in the resonant circuit has sinusoidal voltage and current waveforms, it was reasonable to expect that conventional low-cost film capacitors would be reliable. HP provided capacitor manufacturers with test circuits to demonstrate successful sine-wave operation at high currents. Life tests were begun at HP to explore the possibility that new and unexpected failure mechanisms could be introduced by the high currents. These tests demonstrated that temperature was the prime concern and reliability required just careful thermal design. The capacitor type finally approved uses film-foil construction and polypropylene dielectric. Low-loss polypropylene capacitors and solid copper leads soldered directly to the foil in the capacitors met the reliability re-(continued on page 10)

### Magnetic Components for High-Frequency Switching Power Supplies

### by Winfried Seipel

Designing magnetic components for operation at 200 kHz requires careful consideration of the properties of materials beyond any normally required at much lower frequencies. Each of the major magnetic components in the 65000A Series presented a different set of problems requiring resolution. Our goals were to develop components small in size, design to meet the most stringent of European safety specifications, and allow for the possibility of semiautomated manufacturing to reduce manufacturing costs. The magnetic components of major interest are the resonating inductor, the control reactor (variable control inductor), and the power transformer.

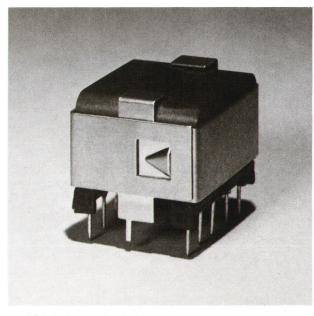

### **Resonating Inductor**

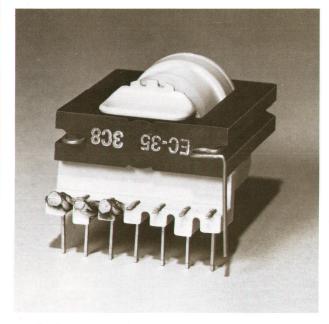

The resonating inductor, Fig. 1, is an ac device that carries the primary circuit resonating current. It was designed using a printed-circuit-mountable coil form and the core was chosen to provide some measure of self shielding. Losses in the device are minimized by operating the core at a flux level appropriate for the ferrite material selected and by selecting a suitable litz wire\* for the winding. To determine the proper flux level the actual core losses for the core selected had to be determined. Published data is generally valid only for specific shapes. It is important to note that core losses are dependent not only on material properties but also on core geometry. The second concern was the selection of the magnet wire. Litz wire is an obvious choice. However, too many strands of very fine wire are expensive and counterproductive, because the percentage of the total volume that is insulation climbs very rapidily as the magnet wire gets finer. If a given volume is available for wire, that volume can very quickly become virtually solid insulation. However, two few strands of a heavy wire will experience an unacceptable increase in resistance because of proximity effect. Although proximity effect is a function of skin \*Litz wire is a type of twisted stranded conductor in which the individual strands are insulated separately

Fig. 1. Resonating inductor.

effect, or more precisely skin depth, the effect can be orders of magnitude worse. Proximity effect is a function of skin depth, conductor diameter, turns per layer, number of conductors per turn, and the number of layers in the coil. The increase of coil resistance from this effect occurs because the magnetic field surrounding each wire in the coil cuts through every other wire in the coil, thereby generating eddy currents. These eddy currents add to and subtract from the normal circuit current to produce a very distorted current distribution.

One additional difficulty required consideration. The air gap in the core structure necessary to adjust inductance properly and prevent saturation causes a large fringing flux through the coil section adjacent to the gap. The fringing flux causes additional coil losses through the generation of additional eddy currents in the wire.

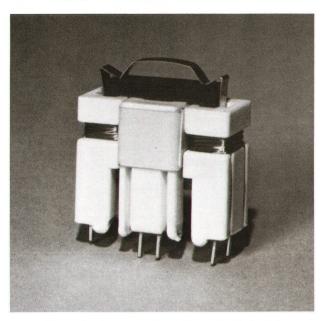

### **Control Reactor**

The control reactor specifications were such that a totally different set of problems from that encountered with the resonating inductor had to be resolved. The device, shown in Fig. 2, is essentially a saturable reactor but with a considerably more gradual saturating characteristic than is normally associated with such a device. It consists of two series-connected reactor coils and one control coil on a pair of E-shaped cores. The control coil is on the center leg and a reactor coil is on each of the outer legs. By the application of a current to the control coil, the impedance of the series-connected reactor coils can be varied. The initial inductance of the reactor is specified to be not less than a certain value given the realities of production and material tolerances. With the application of a specific current to the control winding, the inductance of the reactor coils had to be of a value not greater than a specified amount. In addition, the signal normally fed back to the control coil from the reactor coils in a series-connected device had to be negligible. The design of the device involved the selec-

Fig. 2. Control reactor (variable control inductor).

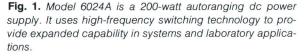

### Fig. 3. Power transformer.

tion of an E core manufactured with a very high-permeability material in a size such that turns and operating flux density could be minimized. Using a high-permeability core material, thereby minimizing reactor turns to achieve the required initial inductance, resulted in minimizing control current requirements. Minimizing control current is extremely important since the availability of this current is severely limited. By keeping the operating flux density in the outer legs of the control reactor low, the legs are essentially kept always in balance. Any flux change in one reactor leg also occurs in the other, thereby preventing flux from being diverted to the control leg. In a typical high-flux reactor, one leg is in saturation while the other is in the linear region. This results in an ampere-turn balance between one and then the other unsaturated reactor coil and the control coil, resulting in an unwanted ac current in the control loop.

An interesting and unusual problem surfaced in the development of this device. Because it is in the feedback path of the control circuit of the power supply, any changes of inductance not related to changes of control signal represent a disturbance for which the control circuit has to compensate. In other words, any mechanical changes in the reactor result in inductance changes, which can result in an unstable circuit. Not only do the core halves have to be securely held together, but any movement of the coils

### **Richard Myers**

Rich Myers graduated from Drexel University in 1962 with a BSEE degree, and began his career as an applications engineer for power transistors and related products. He joined HP in 1973 as a development engineer and helped design 500W, 300W, and 50W switching power supplies, including the 65000A Series. He's now a materials engineer with HP's New Jersey Division and is a member of IEEE. Rich was born in Williamsport, Pennsylvania and now lives in Somerville, New Jersey. He has two children and enjoys reading, travel, and home projects.

### is also unacceptable.

### **Power Transformer**

The problems encountered during the design of the power transformer, Fig. 3, were similar to those experienced in the development of the resonating inductor. Although the power transformer does not have an air gap in its core structure, it does have to carry significantly higher currents in its secondary windings. Due to the creepage and clearance distance and insulation thickness built into the unit, the leakage inductance is fairly high. The use of litz wire with the correct stranding and wire gauge for winding the primary coil is a fairly straightforward solution to minimizing primary coil losses. Litz wire is also used where the secondaries are of the higher-voltage type. However, for the low-voltage winding at the five-volt level, litz wire is impractical, and copper strip is the solution. For the few turns required to provide the necessary secondary voltage, copper strip is the best choice. In the presence of high leakage inductance, more copper losses than would normally be expected occur, because of eddy currents generated by the leakage flux passing through the surface of the strip. Copper strip also suffers from proximity effect but to a lesser degree than litz wire. The same factors as outlined for the resonating inductor govern the magnitude of the effect for strip. Considering the additional losses caused by leakage fields the right combination of strip width and thickness had to be determined.

As in the case of the resonating inductor, core losses had to be determined for the geometry used so that the proper flux level could be found. At 200 kHz the percentage of the total core losses attributable to eddy currents is significant, and eddy currents are a function of geometry.

### Winfried Seipel

Win Seipel joined HP's New Jersev Division in 1969 after receiving his BSEE degree from Newark College of Engineering. His responsibilities have included the design and development of magnetic components, and more recently the management of the magnetic component design group. His work has resulted in a patent on a selfcommutated SCR power supply. Born in Nordenham, Germany, Win enjoys chess and radio controlled model airplanes. He's married, has a daughter, and lives in Lebanon Township, New Jersey.

### **Robert D. Peck**

Bob Peck received his BSEE degree in 1965 from New Jersey Institute of Technology. After two years in the U.S. Army and two years in electronic design, he joined HP's New Jersey Division, contributed to the design of the 62605J and 63000 Power Supplies, and initiated the design of the 65000A Power Supplies. His work has resulted in a patent on a limit cycle controller. Born in Queens, New York, Bob is married, has two children, and lives in Oakridge, New Jersey. He enjoys chess, bicycling, and hiking.

Fig. 10. Simplified schematic of a five-output 65000A Series Power Supply.

quirements for these power supplies.

### Rectifiers

The choice of 200 kHz for the operating frequency was no problem for Schottky rectifiers, but the 65000A Series was expected to provide outputs of 15 volts and more, where Schottky rectifiers could not be used or economically justified. The sinusoidal voltage waveform makes the reverse recovery characteristics less critical. Since a reverse recovery time  $t_{\rm rr}$  of less than 200 ns is considered necessary for 20-kHz power supplies, one might expect that at 200 kHz, rectifiers with a reverse recovery time less than 20 ns would be needed. Instead, at 200 kHz with sine-wave voltages the new low-cost 50-ns rectifiers are quite adequate. In other words, the required  $t_{\rm rr}$  is reduced by only a factor of four even though the operating frequency is ten times higher. Thus low-cost 50-ns rectifiers can be used instead of high-cost 20-ns devices. These 50-ns rectifiers are available at voltages up to 150V, sufficient for 48Vdc outputs.

### Acknowledgments

A large number of people contributed to the design and early production of the 65000A. John Kenny contributed to the electrical design. Mechanical design was by George Kononenko. Techician Pete Graziano put in many extra hours. Special credit is due Tim Kriegel as project leader for pressing the project through to completion, Dilip Amin for his circuit design contributions, and Win Seipel for the design of the magnetic components.

# Laboratory-Performance Autoranging Power Supplies Using Power MOSFET Technology

State-of-the art components and circuit design enable this new generation of laboratory and system supplies to set new standards for performance and flexibility.

### by Dennis W. Gyma, Paul W. Bailey, John W. Hyde, and Daniel R. Schwartz

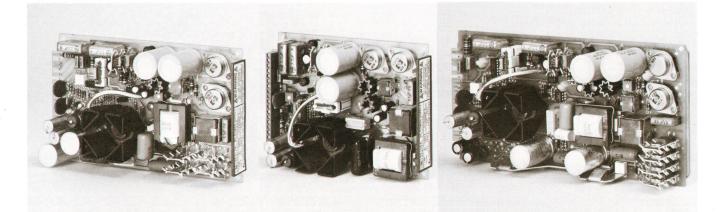

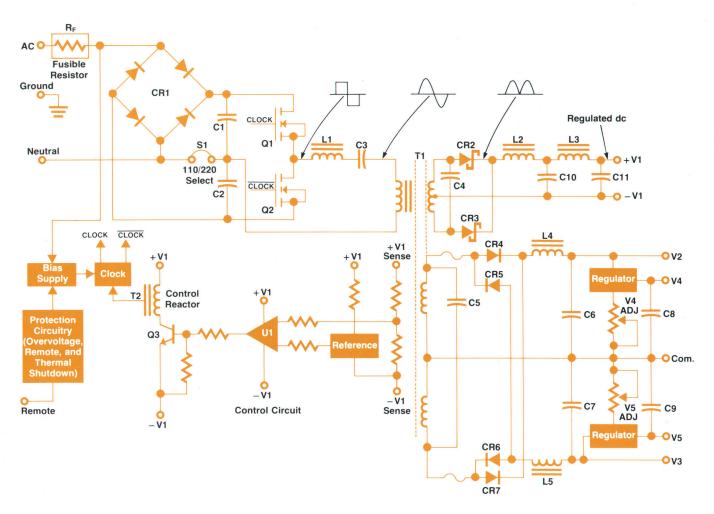

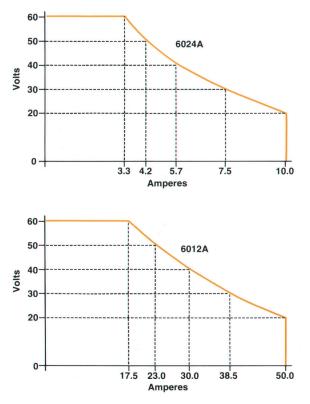

WO NEW AUTORANGING dc power supplies are the first of a new family of precision power supplies based on power MOSFET technology and designed for a variety of laboratory, industrial, and systems applications. Model 6024A (Fig. 1), rated at 200 watts, and Model 6012A (Fig. 2), rated at 1000 watts, deliver rated power over a 20-to-60-volt range, which is why they are termed autoranging. The 6024A will supply a maximum voltage of 60 volts and a maximum current of 10 amperes, but is limited to 200 watts. The 6012A will supply a maximum voltage of 60 volts and a maximum current of 50 amperes, but is limited to 1000 watts. The power supplies' output characteristics are shown in Fig. 3.

These power supplies have a wide variety of applications owing to the flexibility of the autoranging characteristic. On the laboratory bench or in an automatic system, a single supply can satisfy many different biasing requirements. This makes these supplies economically attractive for applications with changing or conflicting requirements, since they are comparable in price to supplies that give maximum power at only one operating point.

The 6024A and 6012A are notable in that they are switch-

**Fig. 2.** Model 6012A is a 1000watt autoranging dc power supply similar in design to the 6024A shown in Fig. 1.

**Fig. 3.** Output characteristics of the 6012A and 6024A power supplies. The curves show maximum output voltage as a function of output current and vice versa.

ing regulated power supplies that achieve laboratory performance. They feature typical energy efficiencies of 80%, a 3-to-1 weight reduction over comparable series regulated units and an order of magnitude increase in programming speed at light loads. Output noise and line and load regulation are at the millivolt level. In addition, both products meet VDE regulations for conducted and radiated electromagnetic interference.

Both products provide such features as overvoltage and overtemperature protection, ten-turn front-panel adjustments for high resolution, and two analog meters for frontpanel voltage and current display. Provision is made at the rear barrier strip for remote voltage or resistance programming in both constant voltage (CV) and constant current (CC) operation. Programming requires 0 to 5 volts or 0 to 2500 ohms for zero to full-scale output in either mode (CV or CC). Also present at the rear barrier strip is a current monitor output that provides 0 to 5 volts for zero to fullscale output current.

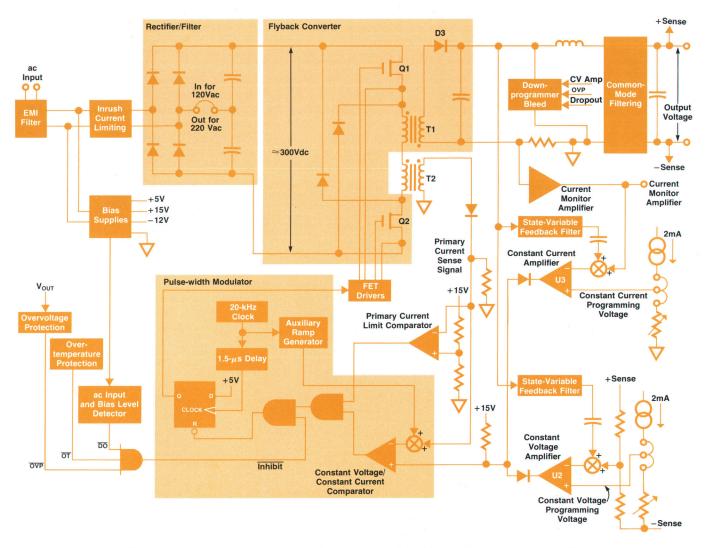

### Switching Technology

The basic topology used in the 6024A and 6012A is the flyback converter (see block diagram, Fig. 4). This topology allows ready control of how much energy is stored in the magnetic field of the power transformer during each clock cycle. The converter operates at constant frequency and regulation is achieved by pulse-width modulation. An operating frequency of 20 kHz allows a dramatic reduction in component size and weight from 60-Hz series-regulated technology, making the products lighter and easier to manufacture. The operating frequency is above the audible range but not high enough to cause power dissipation problems with fixed losses throughout the converter section.

The ac line is brought in through both common-mode and normal-mode EMI filtering. Bias voltages are developed with standard 60-Hz techniques, and power is provided to the inverter through the inrush current limiting section. (Inrush limiting is achieved with thermistors in the 6024A and with limiting resistors shunted by a relay in the 6012A). Following the inrush limiting circuitry is a rectifier/filter section, which is configured as a voltage doubler for 100/ 120Vac operation and as a bridge for 220/240Vac operation. An unregulated dc bus voltage of approximately 300 volts is developed at the output of the rectifier/filter section.

Power FETs Q1 and Q2 are in series and are operated in-phase. The FETs are turned on by the pulse-width modulator, initiating linear current buildup in the magnetizing inductance of power transformer T1. Thus energy is stored in the magnetic field of T1. The primary current of T1 is monitored through current transformer T2 and fed back to the pulse-width modulator as the timing ramp. This timing ramp is compared to the error voltage from either the constant voltage or the constant current control loop, and is also compared to a maximum primary current limit. When the primary current exceeds the lowest of these error voltages, the pulse-width modulator turns off the FETs, interrupting the primary current of transformer T1. The voltage across T1 reverses polarity as a result of the collapsing magnetic field and forces diode D3 to conduct, transferring energy through the output filter to the load. Error amplifiers U2 and U3 maintain either constant voltage or constant current operation by regulating the pulse width of the converter.

The use of the magnetizing current of T1 as the timing ramp for the pulse-width modulator improves the stability of the control loops. It also provides a convenient method of setting both a static and a dynamic limit on how much primary current will be allowed. This translates to defining the maximum output boundary as well as limiting the peak current in each of the power switches Q1 and Q2.

### **Power FETs**

The use of power FETs for switches Q1 and Q2 provides many technical benefits that translate into customer features. For one, the turn-on and turn-off response of the FETs can be made quite rapid by driver circuit design, allowing operation at very small pulse widths (<100 ns), which occur at low output power (light load). This is particularly advantageous in a laboratory supply where bizarre behavior at light loading is undesirable.

In switching rapidly the power FETs dissipate almost an order of magnitude less power in switching loss than a bipolar transistor of similar ratings. In addition, the switching speed can be controlled from the gate, allowing EMI and switching loss to be easily predicted and controlled. The FETs exhibit no secondary breakdown phenomenon, thereby eliminating the need for snubber networks and their power dissipation. The FETs require insignificant static drive power and require energy supplied to the gate only during switching transistions. Therefore, the drive circuits can be simple, efficient, and reliable.

Another aspect of power MOSFETs is that they parallel

Fig. 4. 6012A/6024A block diagram. The design is a flyback converter using power metaloxide-semiconductor field-effect transistors (MOSFETs) as switches.

with great simplicity, sharing current equally, thanks to two mechanisms. Static current sharing is aided by the positive temperature coefficient of the FETs' on resistance,  $R_{ds}(on)$ .<sup>1</sup> Dynamic current sharing during switching is provided by small but roughly equal lead inductances in each source lead of the circuit. Reliable paralleling contributes substantially to the feasibility of a 1000-watt off-line laboratory-performance power supply.

### **Control Circuits**

Since the converter tranfers energy on a cycle-per-cycle basis, power flow to the output can be halted by simply preventing clock pulses from reaching the pulse-width modulator. Circuitry that senses either insufficient bias voltage or dropout of the power line causes the clock pulses to be disabled, preventing energy transfer between the primary and the output. Should the internal thermostats sense unusually high temperature on the power components, clock pulses are again disabled and the converter has zero output. Should the output voltage exceed a customer-preset level, the overvoltage protection circuitry disables the clock pulses, again cutting off the output power. The 6024A and 6012A are designed to operate over a wide range of loads. It was a significant design challenge to stabilize the control loops over their output operating ranges and with reactive loads. State-variable feedback techniques were employed to guarantee stability.

### **Minimum Output Operation**

One problem that arises when applying pulse-widthmodulated switching converters to laboratory power supplies is that inherent delays in control circuits and power switch devices may require that a certain minimum output power be dissipated for proper operation. In fixedoutput supplies, this requirement is often satisfied by adding a load resistor to the supply to dissipate the minimum power. The main disadvantage of this approach is that this power is wasted.

In variable-output supplies, however, the problem becomes much more serious since it is very difficult to dissipate the power at zero output voltage. If the required power is dissipated by a resistor or an electronic load circuit at some low output voltage, the power dissipated at high output voltages becomes excessive. This is a particularly

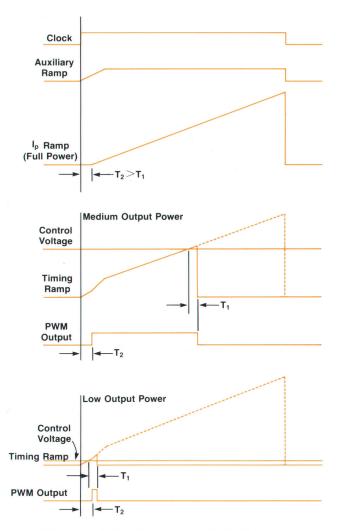

**Fig. 5.** An auxiliary timing ramp added to the primary timing ramp takes effect at low output power so that very narrow, yet controlled pulse widths are produced by the pulse-width modulator (PWM) that switches the MOSFETs on and off. This allows efficient operation at combinations of low output voltage and current.

nasty problem for autoranging supplies that experience large variations in output voltage.

Therefore, it was an important goal in the 6024A and 6012A to employ control circuit techniques and power devices that would allow the generation of very narrow, yet controlled pulse widths in the power converter, so that operation at combinations of low output voltage and current could be obtained with no output bleed.

The method employed to control the on time of the power FETs is to turn on the pulse-width modulator at the beginning of every clock cycle and turn it off when a timing ramp exceeds a control voltage. The timing ramp is a voltage signal that is proportional to the converter primary current, and the control voltage is the error voltage from the control loops.

Any delay  $(T_1)$  from the time when the timing ramp exceeds the control voltage to when the power switch turns off causes the primary current to increase beyond the desired value and transfer more energy to the output than required.

For moderate and high output power, the control loops sense this condition and react by lowering the control voltage until the required on time is achieved. However, for low output power, this correction cannot occur, since the on time cannot be less than the value of the delay  $(T_1)$ .

The delay consists of contributions from the comparator used to compare the ramp with the control voltage, the pulse-width modulator circuits, the power switch driver circuits, and the turn-off delay of the power switch itself. This delay is minimized by using high-speed comparators, pulse-width modulator logic, and driver circuits. In addition, the use of power MOSFETs rather than bipolar transistors significantly reduces the turn-off delay of the power switch. These steps reduce the effect of the delay, but do not eliminate it.

To make it possible to control the on time even when it is very small or zero, an auxiliary ramp is derived from the clock circuit and added to the primary current timing ramp. Two key features of this auxiliary ramp are that it starts at least  $T_1$  earlier than the time the clock turns on the pulsewidth modulator, and that its amplitude is limited to a low value to restrict its operation to small on times (see Fig. 5).

For large on times, the auxiliary ramp does not significantly affect circuit operation. However, for very small on times, the pulse timing is determined entirely by the auxiliary ramp. For very low values of control voltage, the auxiliary ramp can exceed the control voltage and start the turn-off process before the clock turns on the pulse-width modulator. In this way, the pulse-width modulator can produce very narrow pulses in the power converter and eliminate the need for a minimum output bleed.

### Downprogrammer

The 6024A and 6012A are expected to be used as stimulus sources in many automatic test and industrial processes. Throughput is quite important in most of these applications. Accordingly, particular attention was given to the programming speed of these supplies.

The problem of rapidly decreasing the output voltage is accentuated by the fact that these are laboratory switching supplies. To meet the fairly stringent output noise specifications requires a great deal of filtering, resulting in a large capacitance across the output terminals, up to 10,000  $\mu$ F in the 6012A. To change the capacitor voltage rapidly implies a considerable amount of available charging and discharging current. The charging current for up-programming is quite naturally available from the power mesh itself. However, other than the external load, which is unpredictable, there is no inherently available source of appreciable discharge current for downprogramming. Special circuitry had to be employed to meet the programming speed objectives.

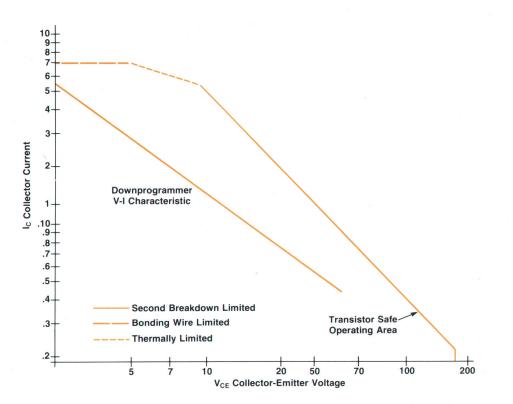

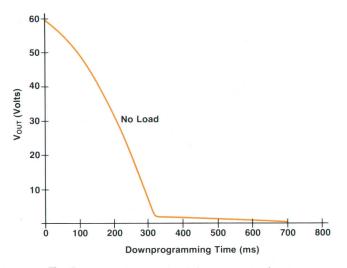

To achieve rapid downprogramming, a power transistor actively discharges the output capacitor. The discharge current is made a function of output voltage to take full advantage of the transistor's safe operating area and to ensure protection from secondary breakdown. The circuit pulls increasingly more current at lower output voltages, giving the downprogrammer circuit an overall negative resistance characteristic (see Fig. 6). This circuit implementation achieves faster downprogramming than a constant-

**Fig. 6.** A downprogrammer with this negative resistance characteristic makes it possible to decrease the output voltage rapidly in automatic test and industrial process control applications.

current or resistive load would, and results in the unusual downprogramming response characteristic shown in Fig. 7. In normal operation the downprogrammer circuit is disabled, so the negative resistance characteristic is not included in the feedback loop.

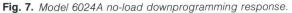

### Systems Interface

Option 002 provides a convenient means for systems integration of either the 6024A or the 6012A by means of a 37-pin rear connector (see Fig. 8).

Six digital output lines that represent power supply status are optically isolated for connection to the customer's data inputs. The lines indicate constant voltage operation, constant current operation, power supply unregulated. overvoltage protection circuit tripped, overtemperature condition, and ac power dropout. Three digital input lines are also optically isolated. These trip the overvoltage circuit, clear the overvoltage circuitry, and provide for remote shutdown. +5, +15, and -15-volt bias supplies referenced to the power supply's bias circuit common are also provided. These bias supplies are particularly useful if the user wants to maintain electrical isolation between the power supply output and a controller. They can be used to power external circuitry such as D-to-A converters that must be referred to the power supply output.

Amplifiers are also provided to allow for current programming of the constant voltage and constant current channels, and for voltage and resistance programming of both channels. Monitor outputs provide 0-5 volts for zero to full-scale output voltage and output current.

By using the 6940B or 6942A Multiprogrammer and standard cards along with Option 002, systems integration of the 6024A and 6012A can be accomplished in minimal time. This can be a very attractive solution where the multiprogrammer (an I/O extender) is already necessary to automate an industrial process. Another advantage of this approach for large systems is that it allows control of multiple power supplies through a single I/O port of the controller.

### Acknowledgments

Ken Woolley, Mike Mercadante, Rick DeRick, and Brian Swarts contributed to the design of the 6024A and Siu Wong, Rich Hilaire, Bill Emmons, and Bob Miller contributed to the design of the 6012A. However, the development was a team effort with close cooperation between both project groups. There are many other people not credited here who contributed to the products' success, and we hope it will suffice to say thanks to those not mentioned.

### Reference

1. D. Gyma, J. Hyde, and D. Schwartz, "The Power MOSFET as a Switch, from a Circuit Designer's Perspective," Proceedings of Powercon 7, Power Concepts, Inc., Ventura, California, 1980.

**Fig. 8.** Option 002 provides a convenient 37-pin rear connector for systems integration of the 6012A or 6024A.

Paul W. Bailey

Paul Bailey joined HP's New Jersey Division in 1974 as a development engineer. He's served as project leader for the 6002A and 6024A Power Supplies, as project manager for laboratory and systems power sources, and as section manager for modular power supply development. His work has resulted in a patent on the downprogrammer circuit used in the 6012A and 6024A. Born in Possum Trot, Kentucky, Paul received his BSEE degree in 1973 from Massachusetts Institute of Technology and his MSEE degree in 1974 from the University of is married, enjoys cardening, and can-

California at Berkeley. Paul is married, enjoys gardening and canning, likes to play basketball and watch Kentucky teams, and spends a good deal of time improving his home in Flanders, New Jersey.

### John W. Hyde

John Hyde was born in Somerville, New Jersey and attended Rutgers University, graduating with BSEE and MSEE degrees in 1973 and 1975. He joined HP in 1975 and contributed to the electrical design of the 6002A and 6024A Power Supplies. Co-author of a paper on using power MOSFETs as switches, he's now a project leader with HP's New Jersey Division. John lives in Parsippany, New Jersey, and enjoys photography, guitar, and gardening.

### Dennis W. Gyma

Dennis Gyma was project leader for the 6012A Power Supply and is now laboratory and industrial section manager with HP's New Jersey Division. A native of Newark, New Jersey, he received his BSEE and MSEE degrees from Rutgers University in 1973 and 1975. With HP since 1975, he's coauthor of a paper on using power MOS-FETs as switches. Dennis is married, has a son, and lives in Netcong, New Jersey. He's an accomplished acoustic and electric guitarist, and he enjoys gardening.

### Daniel R. Schwartz

Dan Schwartz received his BE degree from Cooper Union in 1976 and his MSE degree from Princeton University in 1977. He joined HP in 1977, contributed to the design of the 6012A Power Supply, and is now a project leader with HP's New Jersey Division. A member of IEEE, he's co-author of a paper on using power MOSFETs as switches. A resident of Irvington, New Jersey, Dan enjoys basketball, audio, recording live performances, and spending time in his native New York City.

### SPECIFICATIONS HP 65000A Series 50W Power Supplies

|                            | Outputs*                         |                                                              |                                                                     |                                                         |                       |                |

|----------------------------|----------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|-----------------------|----------------|

| HP<br>Model<br>Number      | Name                             | Nominal<br>Voltage<br>(Vdc)                                  | Maximum<br>Current<br>(Adc)                                         | Typical 50W<br>Application<br>(Adc)                     | Size<br>L×W×H<br>(mm) | Weight<br>(gm) |

| Single Outp                | out                              |                                                              |                                                                     |                                                         |                       |                |

| 65105A<br>65112A<br>65115A | V1<br>V1<br>V1                   | 5<br>12<br>15                                                | 10.0<br>4.2<br>3.3                                                  | 10.0<br>4.2<br>3.3                                      | 180×127×38            | 454            |

| Single +2 (                | Outputs                          |                                                              |                                                                     |                                                         |                       |                |

| 65312A                     | V1<br>V2<br>V3                   | 5<br>+12<br>-12                                              | 10.0<br>1.5<br>1.5                                                  | 5.0<br>1.0<br>1.0                                       |                       |                |

| 65315A                     | V1<br>V2<br>V3                   | 5<br>+15<br>-15                                              | 10.0<br>1.0<br>1.0                                                  | 5.0<br>0.8<br>0.8                                       | 218×127×38            | 510            |

| 65317A                     | V1<br>V2<br>V3                   | 5<br>+18<br>-18                                              | 10.0<br>1.0<br>1.0                                                  | 5.0<br>0.7<br>0.7                                       |                       |                |

| Triple +2 C                | outputs                          |                                                              |                                                                     |                                                         |                       |                |

| 65512A                     | V1<br>V2<br>V3<br>V4<br>V5       | 5<br>+16<br>-16<br>+5 to +12<br>-5 to -12                    | 10.0<br>1.0<br>1.0<br>0.3 to 1.0<br>0.3 to 10                       | 5.0<br>0.4<br>0.5 @ +12<br>0.5 @ -12                    | 264×127×43            | 624            |

| Quadruple +2 Outputs       |                                  |                                                              |                                                                     |                                                         |                       |                |

| 65612A                     | V1<br>V2<br>V3<br>V4<br>V5<br>V6 | 5<br>+16<br>-5 to +12<br>-5 to +12<br>-5 to +12<br>-5 to -12 | 10.0<br>1.0<br>0.3 to 1.0<br>0.3 to 1.0<br>0.3 to 1.0<br>0.3 to 1.0 | 4.0<br>0.7<br>0.6<br>0.3 @ -12<br>0.3 @ -12<br>0.1 @ -5 | 264×127×43            | 624            |

\*V1 is the Main Output. V2 and V3 are semi-regulated extra outputs. V4, V5, and V6 are adjustable over the range given.

INPUT VOLTAGE: 87-127Vac/174-250Vac, 47-63 Hz TEMPERATURE OPERATING: 0-50°C convection cooled 0-70°C fan cooled

STORAGE: -20 to 85°C

CARRYOVER TIME: 25 ms minimum at 115 or 230Vac 10 ms minimum at 104 or 208Vac

EFFICIENCY: 70 to 76% typical

**REMOTE SHUTDOWN:** Latching shutdown via TTL pulse **REMOTE SENSE:** V1 only, ±5% range.

OUTPUT DRIFT: 0.25% maximum 8 hrs after 1-hour warmup

OVERTEMPERATURE: 80±5°C automatic shutdown

SAFETY RECOGNITIONS: UL478, UL114, CSA 22.2/143 and CSA 22.2/154

SAFETY DESIGN TO: VDE 0730/2P and IEC348

EMI: VDE 0871 Class B with external cover and filter

OVERCURRENT PROTECTION: All outputs protected, V1 and V4-V6 thermally protected, V2-V3 fused.

OVERVOLTAGE PROTECTION: V1 and V4-V6 automatic shutdown, V2-V3 voltage clamped.

OTHER OUTPUT SPECIFICATIONS (WORST OF ALL MODELS)

|                                  |                                          |          | REGULATION | PARD    | TEMP COEF         |          |

|----------------------------------|------------------------------------------|----------|------------|---------|-------------------|----------|

|                                  | Output                                   | Line %   | Load %     | Cross % | mV <sub>p-p</sub> | Max %/°C |

|                                  | V1                                       | 0.1      | 0.1        | 0       | 150               | .02      |

|                                  | V2, V3                                   | 5.0      | 12.0       | 7       | 200               | .10      |

|                                  | V4-V6                                    | 2.0      | 2.0        | 0       | 200               | .10      |

| PRICES IN U.S.A.: Unit 1000 qty. |                                          |          |            |         |                   |          |

| Single Output                    |                                          | \$195 \$ | 154        |         |                   |          |

|                                  | Single + 2 Outputs<br>Triple + 2 Outputs |          | \$240 \$   | 190     |                   |          |

|                                  |                                          |          | \$255 \$   | 201     |                   |          |

| Quadruple + 2 Outputs            |                                          | \$265 \$ | 209        |         |                   |          |

|                                  |                                          |          |            |         |                   |          |

### HP Model 6024A Power Supply - 200W

DC OUTPUT: Voltage and current output can be adjusted over the range indicated by using front-panel controls, analog programming, or optional system interface. VOLTAGE: 0-60V CURRENT: 0-10A

Maximum available output power from 20V to 60V is indicated in Fig. 3 on page 12.

| LUAD EFFECT: (Load Regulation).        |                        |  |

|----------------------------------------|------------------------|--|

| VOLTAGE: 0.01% + 3 mV                  | CURRENT: 0.01% + 3 mA  |  |

| SOURCE EFFECT:                         |                        |  |

| VOLTAGE: 0.01% + 2 mV                  | CURRENT: 0.01% + 2 mA  |  |

| PARD (Ripple and Noise) rms/p-p. 20 Hz | z to 20 MHz:           |  |

| VOLTAGE: 3 mV/30 mV                    | CURRENT: 5 mA rms      |  |

| TEMPERATURE COEFFICIENT: Δ/°C at       | fter 30-minute warmup: |  |

| VOLTAGE: $0.01\% + 1 \text{ mV}$       | CURRENT: 0.03% + 1 mV  |  |

| DRIFT: (Stability) change in output                                 | over an 8-hour interval.                                |  |  |  |  |  |  |

|---------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|

| VOLTAGE: 0.03% + 3 mV                                               | CURRENT: 0.03% + 3 mV                                   |  |  |  |  |  |  |

| REMOTE CONTROL (ANALOG P                                            | REMOTE CONTROL (ANALOG PROGRAMMING):                    |  |  |  |  |  |  |

| Resistance necessary for full-sca                                   | Resistance necessary for full-scale output of:          |  |  |  |  |  |  |

| VOLTAGE: $2500\Omega$                                               | CURRENT: $2500\Omega$                                   |  |  |  |  |  |  |

| ACCURACY: 0.8% + 1 mV                                               | ACCURACY: 2.4% + 1 mA                                   |  |  |  |  |  |  |

| Voltage necessary for full-scale of                                 | output of:                                              |  |  |  |  |  |  |

| VOLTAGE: 5 volts                                                    | CURRENT: 5 volts                                        |  |  |  |  |  |  |

| ACCURACY: 0.2% + mV                                                 |                                                         |  |  |  |  |  |  |

|                                                                     | IE: Maximum time for output voltage to change from      |  |  |  |  |  |  |

| 0V to 60V or 60V to 2V and sett                                     |                                                         |  |  |  |  |  |  |

| UP: Full Load (18 $\Omega$ ) 200 ms                                 |                                                         |  |  |  |  |  |  |

| No Load 200 ms                                                      |                                                         |  |  |  |  |  |  |

| OVERVOLTAGE PROTECTION: Trip voltage adjustable from 2 to 64 volts. |                                                         |  |  |  |  |  |  |

| AMPLIFIED CURRENT MONITOR: 0-5V monitor output for 0-10A output.    |                                                         |  |  |  |  |  |  |

| EMI SPECIFICATIONS: Meets VDE 0871/6.78 Level A.                    |                                                         |  |  |  |  |  |  |

|                                                                     | plies with IEC 348, VDE 0411, CSA 556B, CSA C22.2       |  |  |  |  |  |  |

| #0-1975.                                                            |                                                         |  |  |  |  |  |  |

| TEMPERATURE: OPERATING: 0                                           |                                                         |  |  |  |  |  |  |

| STORAGE: -40                                                        |                                                         |  |  |  |  |  |  |

| AC INPUT: 104-127Vac 48-63 Hz,                                      |                                                         |  |  |  |  |  |  |

| WEIGHT: Net 5.4 kg (12 lb). Shipp                                   |                                                         |  |  |  |  |  |  |

|                                                                     | ame as system interface option for 6012A except voltage |  |  |  |  |  |  |

| accuracy is 0.3% + 7 mV and co<br>PRICES IN U.S.A.:                 | Jrrent accuracy is 1% + 2 mA.                           |  |  |  |  |  |  |

|                                                                     |                                                         |  |  |  |  |  |  |

| 6024A Power Supply, \$875.                                          |                                                         |  |  |  |  |  |  |

| Option 002: System Interface, \$3                                   |                                                         |  |  |  |  |  |  |

| Option 100: 87-106Vac, 48-63 H                                      | z, N/C. (Output derated to 50V, 150W.)                  |  |  |  |  |  |  |

HP Model 6012A Power Supply - 1000W

Option 220: 191-233Vac, 48-63 Hz, N/C. Option 240: 208-250Vac, 48-63 Hz, N/C.

DC OUTPUT: Voltage and current output can be adjusted over the range indicated by using front-panel controls, analog programming, or optional system interface. VOLTAGE: 0-60V CURRENT: 0-50A

Maximum available output power from 20V to 60V is indicated in Fig. 3 on page 12. LOAD EFFECT: (Load Regulation):

| VOLTAGE: 0.01% + 5 mV                                  | CURRENT: 0.01% + 5 mA                   |

|--------------------------------------------------------|-----------------------------------------|

| SOURCE EFFECT:                                         |                                         |

| VOLTAGE: 0.01% + 3 mV                                  | CURRENT: 0.01% + 5 mA                   |

| PARD (Ripple and Noise) rms/p-p. 20 Hz to 2            | 0 MHz:                                  |

| VOLTAGE: 5 mV/50 mV                                    | CURRENT: 25 mA rms                      |

| TEMPERATURE COEFFICIENT: Δ/°C after 3                  | 0-minute warmup:                        |

| VOLTAGE: 0.01% + 2 mV                                  | CURRENT: 0.01% + 3 mA                   |

| DRIFT: (Stability) change in output over an 8-         | hour interval.                          |

| VOLTAGE: 0.03% + 5 mV                                  | CURRENT: 0.03% + 5 mA                   |

| REMOTE CONTROL (ANALOG PROGRAMM                        |                                         |

| Resistance necessary for full scale output of          |                                         |

| VOLTAGE: 2500 $\Omega$                                 | CURRENT: $2500\Omega$                   |

| ACCURACY: 1% + 3 mV                                    | ACCURACY: 2.5% + 10 mA                  |

| Voltage necessary for full-scale output of:            |                                         |

| VOLTAGE: 5 volts                                       | CURRENT: 5 volts                        |

| ACCURACY: 0.3% + 3mV                                   | ACCURACY: 1% + 10 mA                    |

| PROGRAMMING RESPONSE TIME: Maximu                      |                                         |

| 0V to 60V or 60V to 2V and settle within 20            |                                         |

| UP: Full Load $(3.4\Omega)$ 120 ms                     | DOWN: Full Load $(3.4\Omega)$ 400 ms    |

| No Load 120 ms<br>OVERVOLTAGE PROTECTION: Trip voltage | No Load 1.2 s                           |

| AMPLIFIED CURRENT MONITOR: 0-5V mon                    |                                         |

| EMI SPECIFICATIONS: Meets VDE 0871/6.7                 |                                         |

| SAFETY SPECIFICATIONS: Complies with IE                |                                         |

| #0-1975.                                               |                                         |

| TEMPERATURE: OPERATING: 0 to 50°C.                     |                                         |

| STORAGE: -40 to +75°C.                                 |                                         |

| AC INPUT: 104-127Vac 48-63 Hz, 24A rms m               | aximum.                                 |

| WEIGHT: Net 15 kg (33 lb). Shipping 16 kg (3           | 35 lb).                                 |

| SYSTEM INTERFACE OPTION REMOTE CO                      | NTROL (ANALOG PROGRAMMING):             |

| Sink current necessary for full scale of:              |                                         |

| VOLTAGE: 2 mA                                          | CURRENT: 2 mA                           |

| ACCURACY: 0.4% + 9 mV                                  | ACCURACY: 1.1% + 15 mA                  |

| ISOLATION: Status and control lines; 600               | /dc max from equipment ground, from the |

| power supply output or from each other.                |                                         |

| PRICES IN U.S.A.:                                      |                                         |

| 6012A Power Supply, \$1550.                            |                                         |

| Option 002: System Interface, \$300.                   |                                         |

| Option 100: 90-105Vac, 48-63 Hz, N/C. (Ou              | tput derated to 50V, 750W.)             |

| Option 220: 191-233Vac, 48-63 Hz, N/C.                 |                                         |

| Option 240: 208-250Vac, 48-63 Hz, N/C.                 |                                         |

| MANUFACTURING DIVISION: NEW JERSEY                     |                                         |

| Green Pond R                                           |                                         |

| Hockaway, Ne                                           | w Jersey 07866 U.S.A.                   |

# The Vertical Power MOSFET for High-Speed Power Control

A vertical semiconductor device structure provides a power MOSFET that can switch high currents and voltages very rapidly. This makes it useful for power supplies, pulse drivers, and switching amplifiers.

### by Karl H. Tiefert, Dah Wen Tsang, Robert L. Myers, and Victor Li

OWER AND FREQUENCY are natural electronic enemies. In a variety of detailed technical ways, as well as in fundamental ones, the speed of operation of a device is limited by its operating power level. As new technology is developed, old speed and/or power barriers are overcome and new limits are established, as described qualitatively in Fig. 1.

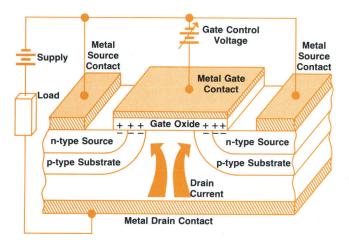

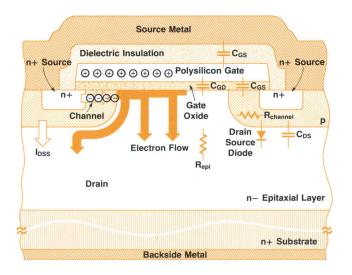

A new component development leading to a major shift in power-frequency performance is the vertical power MOSFET (metal-oxide-semiconductor field-effect transistor). In this device, the best features of earlier technologies and innovative device design are combined with state-ofthe-art MOS wafer fabrication techniques to achieve performance that in some applications can be an order of magnitude better than that previously attainable.

### **Semiconductor Power Switches**

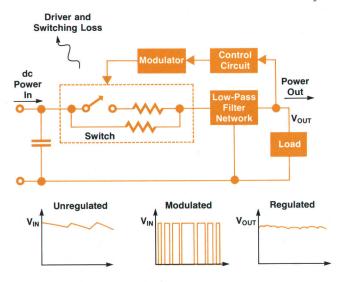

Designers and manufacturers of power conversion and control equipment are constantly seeking a more efficient switch. This is because the efficiency of controlling or converting electrical power using modern pulse modulation techniques as illustrated in Fig. 2 is directly related to the efficiency of the switch. A source of dc power (usually rectified ac line voltage) is modulated by the switch

1 ns 10 New Planar Switching Speed 100 Power MOSFE 1µs 10 Power Bipolar ransisto 100 1 ms Thyristor 10 10 102 103 104 0.1 **Power Handling (Watts)**

**Fig. 1.** Speed versus power for various power semiconductor devices. Technology advances are generally upward to the right.

to regulate the amount of power supplied to the load. Output voltage is sensed at the load by the control circuit which in turn feeds a control signal back to the pulse modulator. The pulse modulator controls the amount of power delivered to the load by varying the switch's duty cycle by either pulse-width or repetition-rate modulation. An energy analysis of this system provides a definition of an ideal switch against which devices can be measured. To have zero power consumption, an ideal switch has zero resistance in the on state and zero current leakage in the off state, and makes the transition between these states in zero time. The ideal switch also requires zero drive power and is capable of unlimited repetition rates. The latter feature allows reduction of magnetic and filter component sizes. As switch characteristics approach ideal values, power control and conversion equipment can be made more efficient, smaller, and usually less expensive.

Until recently, conventional solutions to the problem of providing industry with an ideal switch (or at least a practical one) have been realized in the form of thyristors, bipolar transistors, and planar field-effect transistors. Each of these devices has advantages and limitations.

The thyristor (SCR, triac, etc.) is a bistable solid-state device that blocks the flow of current until turned on by a

**Fig. 2.** A block diagram of a basic power controller using an ideal switching element.

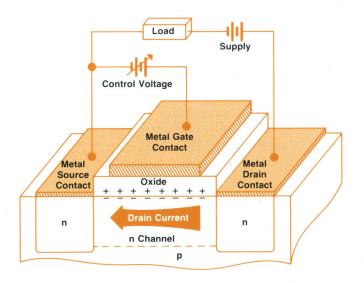

**Fig. 3.** Simplified cross section of a planar MOSFET. Current flows laterally from the drain under the gate to the source.

small control signal. Once turned on, the thyristor remains on until the supply voltage is removed or reversed in polarity. While these devices are able to control large amounts of power (up to hundreds of kilowatts), they are usually limited to switching frequencies of only a few kilohertz. The speed limitation and inability to be turned off by a control signal severely limits their general application to direct control of power to a load from the ac power line. Common applications are motor speed controllers and light dimmers.

The workhorse of the power control industry has been the bipolar power transistor. This ubiquitous device has been used for almost every conceivable power control application from servo controls to switched-mode amplifiers. The bipolar power transistor functions in the same way as its small-signal counterpart, but is physically larger to enable

**Fig. 4.** The HP Model HPWR-6501-Series Power MOSFETs are mounted in TO-3 packages as shown. Units are 100% tested before shipment.

# **Power MOSFET Performance** Useful for Many Applications

The vertical power MOSFET combines the circuit advantages of planar FETs with the surface packing density of vertical device structures to offer efficient and convenient control of high currents and voltages. Because of its exceptional switching speed as a majority carrier device, it can be operated at far higher switching rates than any of the alternative devices at equivalent power levels. The applications that can benefit from this additional performance are:

- Switching power supplies. The fast switching speed of the power MOSFET reduces switching losses in switching power supplies by reducing the period of time during which significant voltage and current occur simultaneously at the device terminals. This speed allows higher repetition rates that can be used to reduce the size of transformers and filter elements, thereby reducing size, weight and cost of associated power supply circuitry. The simplified drive requirement (capacitance as compared to base charge storage in the bipolar transistor, for example) results in simpler, less expensive drive circuits. Majority-carrier operation avoids negative resistance temperature coefficients and hence avoids thermal runaway, secondary breakdown, and other deleterious effects, while allowing devices to be paralleled without concern. These uncomplicated modes of operation lead to rugged performance. See the two articles on MOSFET switching power supplies in this issue for further details (pages 3 and 11).

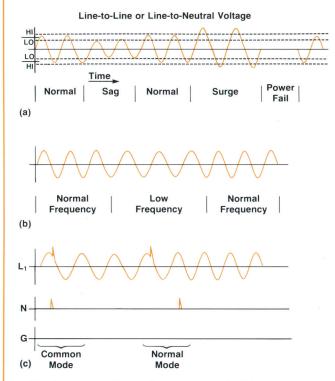

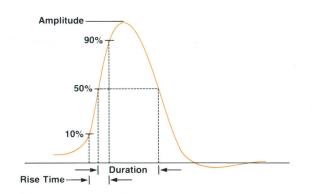

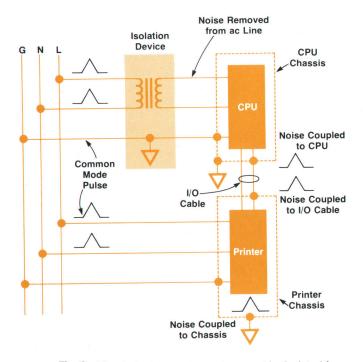

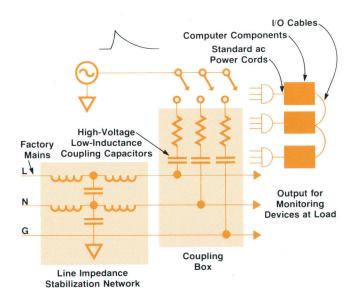

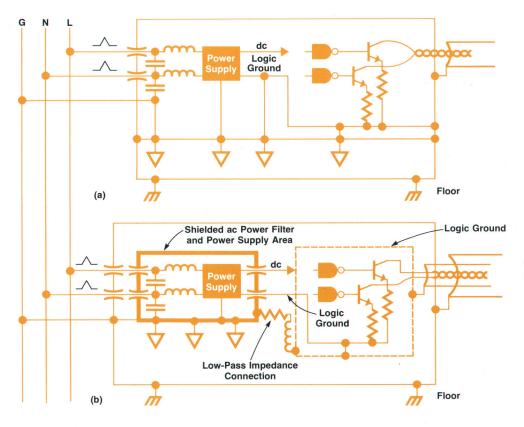

- Pulse drivers. The power MOSFET pulse response is excellent. Transition speeds are in the nanosecond range for kilowatt power levels, and the absence of storage delays and other minority-carrier effects offers both pulse fidelity and device ruggedness. Straightforward input and output impedance makes pulse-circuit matching a relatively easy task.